Abstract

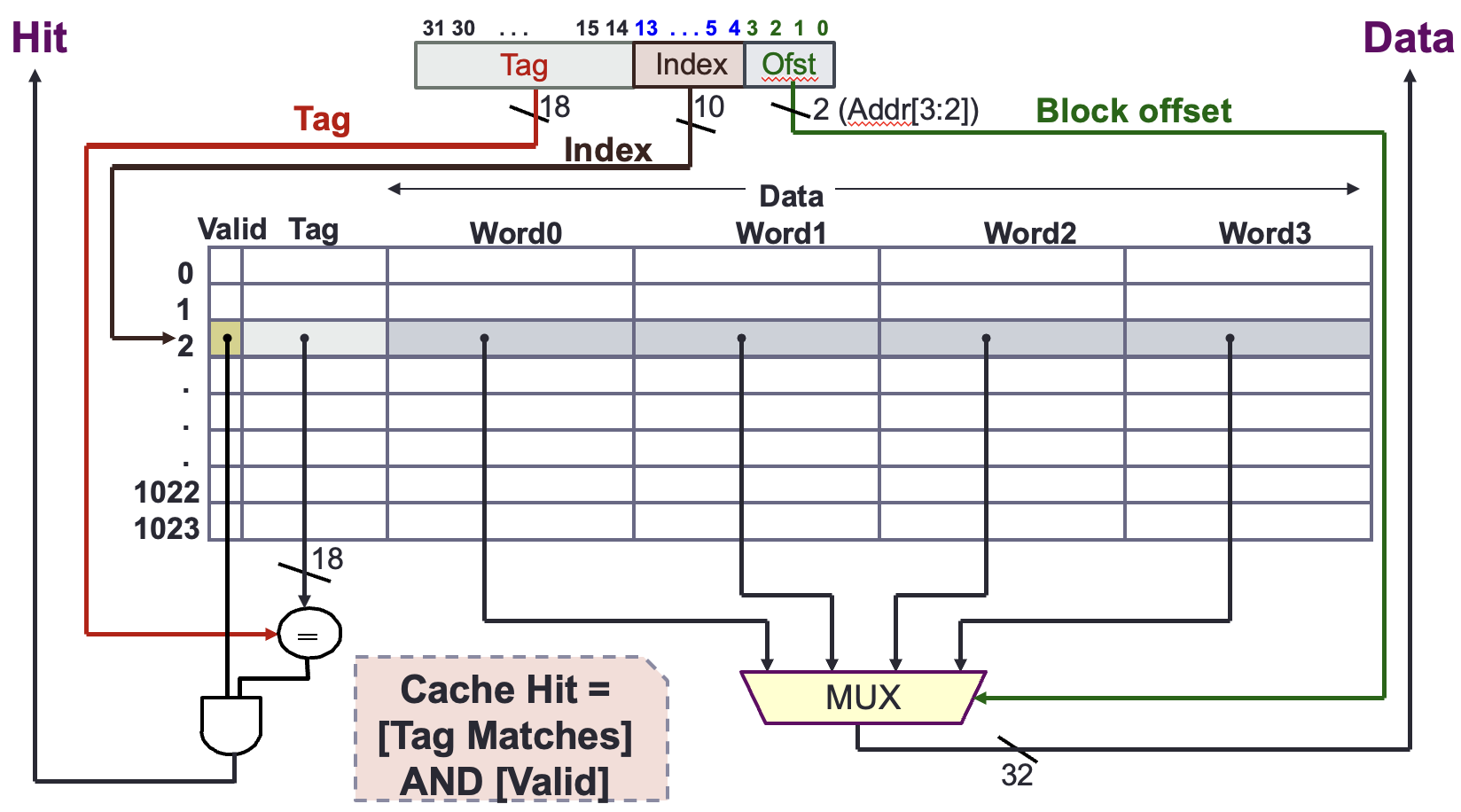

+-----------------------------------------------------------+

| 32-bit Address |

+-----------------------+------------+----------+-----------+

| Block | Offset |

| Number | |

| (28 bits) | (4 bits) |

+-----------------------+------------+----------+-----------+

| Cache | Cache | Word | Byte |

| Tag | Index | Offset | Offset |

| (18 bits) | (10 bits) | (2 bits) | (2 bits) |

+-----------------------+------------+----------+-----------+

- In the above example, the CPU Cache has Cache Line, each contains words, each word is bytes

- Each cache line is indexed with a cache index. This allows a CPU cache with limited storage to cover the entire main memory because multiple physical addresses can map to the same cache line. However, this mapping also means that multiple physical addresses share the same cache line. To distinguish between these different addresses, each cache line includes a cache tag that identifies the specific physical address currently stored in that line

How is data read?

- We first use the cache index to locate the cache line

- We use the valid bit to check if the cache line contains data. If it does, and the tag matches the given address, we can select the word needed using the word offset with a help of a Multiplexer

- Otherwise, there is a cache miss.